掌握SDSoc 開啟Zynq應用開發的“高速通道”

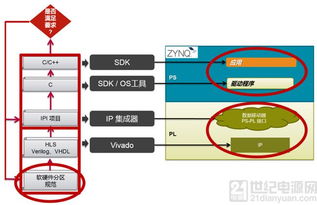

在嵌入式系統與異構計算領域,Xilinx的Zynq系列SoC(片上系統)憑借其獨特的ARM處理器與FPGA可編程邏輯的緊密結合,為高性能、低功耗應用提供了強大的平臺。傳統的Zynq開發流程往往需要在PS(處理系統)端的軟件編程與PL(可編程邏輯)端的硬件設計之間反復切換、手動優化,門檻較高且耗時費力。

這時,SDSoc(Software-Defined System-On-Chip,軟件定義片上系統)的出現,無疑為開發者指明了一條顯著的“捷徑”。它并非繞過必要的設計思考,而是通過智能化的工具鏈,極大地簡化了從算法到高效硬件實現的路徑。

SDSoc的核心優勢:提升抽象層級

SDSoc的本質是一個高層次綜合(HLS)與系統級協同設計的開發環境。它的“捷徑”特性主要體現在以下幾個方面:

- 以C/C++為中心的設計流程:開發者無需精通VHDL或Verilog等硬件描述語言。只需使用熟悉的C、C++或OpenCL編寫算法代碼,SDSoc便能自動分析代碼,將計算密集型函數或循環智能地綜合成硬件加速器(在PL中實現),而其余部分則作為軟件在ARM處理器上運行。這大幅降低了硬件加速的開發門檻。

- 自動化的系統集成:SDSoc工具鏈自動處理了最繁瑣的部分——硬件加速器與處理器系統的集成。它會自動生成必要的總線接口(如AXI)、DMA控制器、驅動程序以及軟件API,省去了開發者手動搭建通信橋梁的大量工作,確保了軟硬件之間的高效數據流通。

- 智能化的設計空間探索:SDSoc提供性能分析與估計工具。開發者可以通過添加編譯指示(Pragmas)到源代碼中,指導工具進行不同的硬件實現優化(如流水線、數據流、數組映射等),并快速評估不同方案對性能、資源利用率的影響,從而在短時間內找到最優的軟硬件劃分方案。

- 快速原型驗證與迭代:憑借其高度自動化的流程,SDSoc支持快速地將算法模型轉化為可運行在Zynq硬件上的系統。這使得開發者可以早期驗證功能正確性,并基于實際性能數據進行快速迭代優化,縮短了開發周期。

這條“捷徑”通向何方?

SDSoc尤其適用于以下場景:

- 算法加速:如圖像處理、計算機視覺、機器學習推斷、數字信號處理(DSP)、加密解密等包含大量并行計算或定制數據流的算法。

- 系統原型快速搭建:當需要驗證一個包含復雜計算的概念時,SDSoc能最快地讓它在真實硬件上跑起來。

- 軟件工程師涉足硬件加速:為軟件團隊開啟了一扇利用硬件性能的大門,無需深度轉型為硬件工程師。

捷徑上的“注意事項”

天下沒有免費的午餐。要高效利用SDSoc這條捷徑,開發者需要注意:

- 編寫“可綜合”的代碼:并非所有C/C++代碼都能被高效地綜合為硬件。需要遵循HLS的編碼規范,例如關注循環結構、數據依賴、接口類型等。

- 理解硬件基本概念:雖然無需手動編寫RTL,但了解流水線、并行、資源(BRAM、DSP、LUT)等基本硬件概念,對于添加有效的Pragmas指導優化至關重要。

- 最終性能與資源權衡:全自動流程產生的設計在極端優化場景下,可能仍不及經驗豐富的工程師手工打磨的RTL設計。但對于大多數應用,SDSoc能在開發效率與性能提升之間取得極佳的平衡。

結論

SDSoc作為Zynq應用開發的強大工具,確實是一條值得擁抱的“捷徑”。它將開發者從繁瑣的低層次系統集成中解放出來,專注于算法創新和系統級優化。通過提升設計抽象層級,它顯著降低了Zynq平臺硬件加速的開發難度與時間成本,使得更多領域的工程師能夠釋放Zynq異構計算的巨大潛力。對于追求快速產品上市或希望高效實現算法硬件加速的團隊而言,熟練掌握SDSoc,無疑是贏得先機的關鍵一步。

如若轉載,請注明出處:http://www.openedv.com.cn/product/72.html

更新時間:2026-04-03 18:29:32